The versatility of the controller stems from the use of a Motorola 24-bit DSP56303 digital signal processor, located on the DSP timing board with support circuitry for its internal and external peripherals. On-chip resources permit the DSP to run code from an internal 4K program memory, and to use two internal 2K data memories for storage. External 64K SRAM memory is available as necessary. The DSP runs at an internal clock frequency of 80 MHz, phase locked to an external 10 MHz oscillator. DSP instructions are typically executed in one 25 ns instruction cycle. The speed of the processor allows the CCD clocking sequences to be directly generated by the DSP under program control.

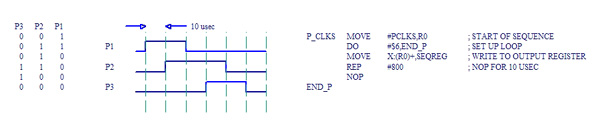

To perform an operation such as a serial or parallel shift the DSP steps though and writes the sequence of data words into an external 24-bit register via the DSP external bus [D0..D23]. Each sequence fragment is held in the external register until it is overwritten by the next fragment after a preset number of clock cycles, as coded into the DSP control software. The number of clock cycles (hold time) determines the timing of the clocks to the CCD. The time resolution of the clocking sequences is 25 ns. Program code and the clock sequence fragments are stored in the flash memory and loaded into the DSP on-chip memory during power up.

Each bit of the 24-bit DSP word represents one of the CCD control signals. With 24 bits, there are control signals for two sets of parallel clocks [ P1A-P2A-P3A and P1B-P2B-P3B] and the two sets of serial clocks [S1R-S2R-S3R and S1L-S2L-S3L]. These can be used for two independent CCDs, for a frame transfer CCD, or for dual-channel readout of a single CCD. Other signals control the pixel conversion functions such as the dual slope integrator on/off and polarity, integrator capacitor reset, input clamp, and A/D converter start [FINT+, FINT-, FRST, IPC, /CONVST]. Spare bits allow additional signals to be added to accommodate different devices, as necessary.

Normally, for parallel transfers or frame transfer, the serial clocks and dual slope integrator control lines are held in a pre-specified state dictated by the CCD architecture. Similarly, the serial transfers require that the parallel clock lines be held in a specified state, possibly an MPP mode to reduce the dark current. This allows all control lines to be generated simultaneously as one 24-bit word.

A programmable logic device (EPLD) provides address decoding to allow the external clock register, and external analog-to-digital converter (ADC) and digital-to-analog converter (DAC) peripherals to be memory mapped. This simplifies the software a great deal by allowing each peripheral to be accessed as if it were a simple memory location. External peripherals are selected by a combination of a slot-select signal, and a three bit address (which is decoded on each individual pcb). During setup, the DSP writes to each individual DAC to set up the appropriate clock and bias voltages.

Communication with a host computer is available via both a fast bi-directional serial link and a full-duplex optical link. The DSP synchronous serial interface (SSI) transfers data via a bidirecitonal RS-422/485 at up to 20 Mbps to/from a PCI interface, up to 100m away. The optical link runs at 80 Mbps over multimode fiber.

Greg Burley (burley@obs.carnegiescience.edu)

Ian Thompson (ian@obs.carnegiescience.edu)