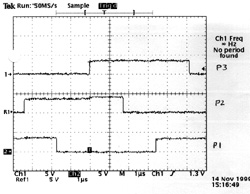

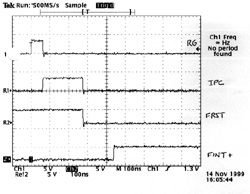

Parallel clocks

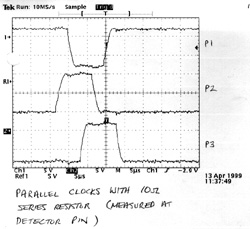

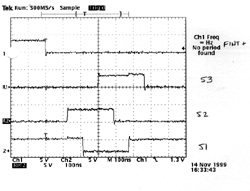

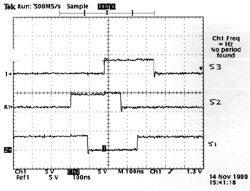

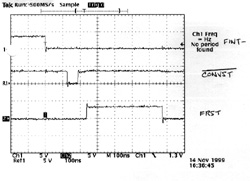

Serial + dual_slope clocks

|

|

|

|

The four figures show o'scope

traces for the various serial clock and dual-slope converter related

signals. Each trace is set at 100ns/div.

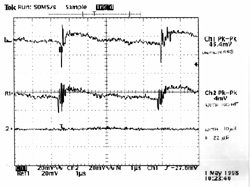

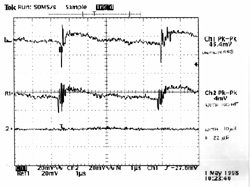

Power filtering

The power filtering figure shows three traces -- the unfiltered DC-DC converter output, the output with a filter capacitor installed, and with an LC filter.

Operating voltages

The power filtering figure shows three traces -- the unfiltered DC-DC converter output, the output with a filter capacitor installed, and with an LC filter.

Operating voltages

CCD47-20

Operating voltages

| Signal |

Symbol |

Voltage |

| Image area Parallel clocks |

IM3, IM2,

IM1 |

+3V -9V |

| Storage area Parallel clocks |

ST3, ST2,

ST1 |

+3V -9V |

| Serial clocks |

R3, R2, R1 |

+2V -8V |

| Reset gate |

RG |

+3V -9V |

| Dump gate |

DG |

+3V -9V |

| Output drain |

OD |

+20V |

| Reset drain |

RD |

+8V |

| Output gate |

OG |

-6V |

| Substrate |

SUB |

GND |

Greg Burley (burley@obs.carnegiescience.edu)

Ian Thompson (ian@obs.carnegiescience.edu)